Mikropropesor I8051 - I4051 - I2051

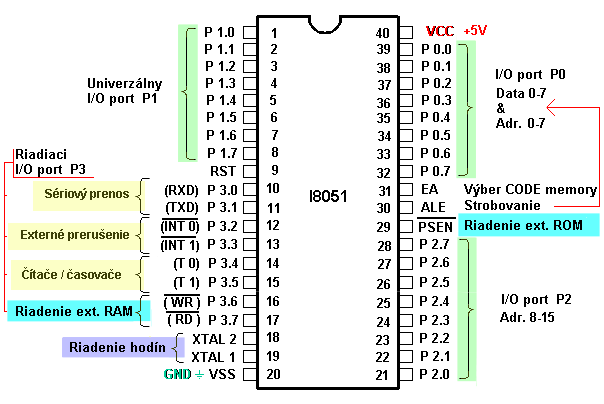

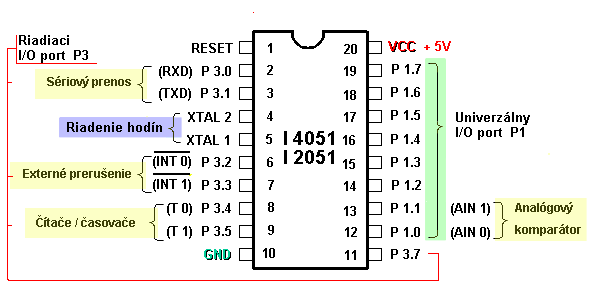

Schéma vnútornej blokovej štruktúry mikroprocesora I8051 a jej jednoduchších klonov I4051 a I2051 sa líši len v tom, že jednoduchšie verzie nemajú vyvedené porty paralelné 8 bitové porty P0 a P2 (používané na exportovanie dátovej a adesnej zbernice pri rozširovaní konfigurácie o externé prvky RAM, ROM a podbných externých zariadení).

Stručná charekteristika

Špecialitou mikroprocesora I8051 je to, že je ho vnútorná štruktúra je zároveň štruktúrou mikropočítača. Obsahuje vnútorné zbernice Riadiacu, Adresnú a Datovú, obsahuje CPU s ALU (aritmetickou a logickou jednotkou), dve pamäte RAM pre uloženie dát a ROM (EPROM) pre uloženie programu (Harwardská koncepcia), dva pracovné čítače a komunikačný obvod UART pre sériovú komunikačnú linku. Pre paralenlú komunikáciu procesor obsahuje 4 univerzálne obojsmerné vstupno výstupné porty P1,P2,P3 a P4 (verzie I4051 a I2051 len 2 porty P1 a P3).

Mikropočítač I8051 umožňuje prepojenie vnútorných zberníc cez porty P0,P2 a P3 a ich využitie pre rozšírenie vnútornej konfigurácie o ďaľšie externé prvky. Dajú sa takto doplniť RAM a ROM pamäte, a ďalšie prvky riaditeľné cez zbernice. Port P0 striedavo slúži na prenos jednak obsahu dátovej zbernice a jednak nižších 8 bitov 16bitovej adresnej zbernice. Aktuálny obsah adresy v registri P0 strobuje signál ALE (Adress low enable) aktorý a je synchronizovaný s ďaľšími riadiacimi vodičmi PSEN*, RD* a WR* určenými na riadenie externých RAM, ROM, a iných zariadení. Port P2 trvale slúži na prenos vyšších 8 bitov adresnej zbernice a port P3 prenáša signály riadiacej zbernice RD*, WR* a signálne vodiče ďaľších interných zariadení Radiča prerušení, Čítačov a Sériového kanála.

Špecialitou RAM pamäte je že mapuje registre používané CPU a jej

ALU do adresného priestoru nazývaného REGISTRE SPECIÁLNYCH FUNKCIÍ

(SFR). Okrem toho RAM pamäť obsahuje 4 banky 8 bitových pracovných

registrov R0-R7, ktoré sa prepínajú nastavením banku pomocou 2 bitov RS1

a RS2 v stavovom registri (PSW - Program status WORD)

Špecialitou RAM pamäte je že mapuje registre používané CPU a jej

ALU do adresného priestoru nazývaného REGISTRE SPECIÁLNYCH FUNKCIÍ

(SFR). Okrem toho RAM pamäť obsahuje 4 banky 8 bitových pracovných

registrov R0-R7, ktoré sa prepínajú nastavením banku pomocou 2 bitov RS1

a RS2 v stavovom registri (PSW - Program status WORD)

Funkcie PINOV

EA - (External Access) Hardwarové nastavenie režimu práce s pamäťovým priestorom a prepínanie do programovacieho režimu u EPROM verzií procesora. Testuje sa jediný raz pri skončení signálu RESET a jeh dynamická zmena počas priebehu práce nie je možná! Má význam len pre I8051 a ovplyvňuje používanie CODE memory v ktorej sa nachádza programový kód. V prípade že EA = 0 tak sa program vykonáva iba z vonkajšej CODE pamäti. Ak sa EA = 1 potom sa kombinuje vnútorná pamäť pre kód od adresy 0-0FFFH a externá pamäť 1000H-FFFFH. Prekrytá externá pamäť internou pamäťou sa pristupuje cez rozdielne inštrukcie. Signal musí byť bezpečne t.j. jednoznačne ošetrený! Pri procesore s pamätou EPROM sa vstup EA používa na prechod do programovacieho režimu. Vtedy sa na tento vstup privedie Up programovacie napätie (určuje ju výrobca v technickej dokumentácii) a vyvolá sa RESET. Po skončení nulovacieho signálu RESET procesor vstúpi do programovacieho režimu.

UNIVERZÁLNE V/V KANÁLY P0 - P3 sú tvorené špeciálnym zapojením registrov, ktoré umožňuje využívať porty oboma smermi. Špecialita tohto zapojenia umožňuje maskovať vstupy nastavením portov. Aby sme mohli prečítať vstupujúci údaj z pinu daného portu, musíme najprv na port vyslať logickú "1". Pri reštarte počítača sa tento stav nastavuje automaticky.

ALE - Adress Low Enable - Pretože nižších 8 bitov adresovej zbernice sa musí deliť o port P0 s dátovou zbernicou, rieši sa to v priebehu inštrukčného cyklu tak, že najprv sa na porte objaví adresa a jej prítomnosť signalizuje a súčasne zostupnou hranou strobuje signál ALE. Ten sa využíva na zápis adresy do pomocných externých registrov. Po odovzdaní adresy sognál ALE sa vracia na pôvodnú hodnotu "1" a port P0 je uvolnený pre dátovú zbernicu.

PSEN*,RD*,WR* - Sú riadiace signály, ktoré sú generované pri vykonávaní inštrukcií MOV, MOVX a MOVC. Spolu s Adresnou a Dátovou zbernicou (Porty P0 a P1) a so signálom ALE sa podielajú s komunikáciou s externou ROM pamäťou (PSEN* - čítanie) a s externou RAM pamäťou (RD*- čítanie, WR*- zápis).

Ovody INT0*, INT1* Externého prerušenia - Po prechode z úrovne 1 do úrovne 0 a po povolení prerušenia riadiacimi registrami, vykonajú systémové volanie CALL na systemových adresách 0003H (INT0) a 0013H (INT1), ktoré obslúži prerušenie. ... Pokračovanie

Registre špeciálnych funkcií

sú umiestnené v časti RAM pamäti adresovanej od adresy 80H do adresy F0H. Do tejto RAM sa mapujú všetky registre procesora. B, ACC, PSW, ...

REGISTRE

Príklady rozšírenia systému

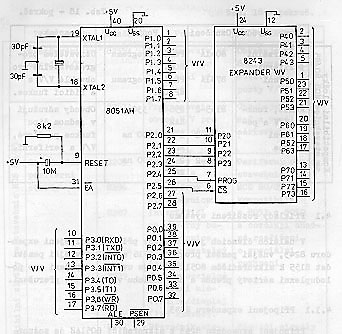

V ďalších článkoch sú uvedené príklady pripojení expanderu 8243,

externej pamäti programu 2716 a 2732 a externej pamäti dat 8155 k

mikropočítaču 8051. Ďalej je uvedené zapojenie pre poloduplexný sériový

prenos a pre obsluhu viac zdrojov prerušenia

Pripojenie expandera 8243:

Pripojení expandera 8243 k mikropočítaču 8051AH je znázornené na tomto obrázku:Obr 47 str 118. V tomto zapojení sa port 2 využívá pre paralelný vstup alebo výstup a pre generovanie riadiacich signálov nutných pre ovládanie expandera. Softwarový ovládač, ktorý respektuje rozhraní obvodu 8243, môže byť vytvorený například takto:

.

.

.

;VSTUPNÉ DÁTA Z EXPANDERU V/V 8243

;SÚ PRIPOJENÉ K P2.3 - P2.0

;P2.5 - SIGNÁL CS/

;P2.4 - SIGNÁL PROG

;P2.7, P2.6 SÚ VYUŽITÉ AKO VSTUPY

;OBSAH PORTU 2 SA CÍTA DO AKUMULÁTORA Acc

;

VSTUP: ORL A,#11010000B

;RIADIACA INFORMÁCIA PRE 8243

MOV P2,A

;JEJ ZÁPIS DO P2

CLR P2.4

;ZOSTUNÁ HRANA SIGNÁLU PROG

CRL P2,#00001111B

;NASTAVENIE P2.3 - P2.0 PRE VSTUP

MOV A,P2

;ČÍTANIE VSTUPNÝCH DÁT

SETW P2.4

;NÁVRAT PROG NA LOGICKÚ HODNOTU 1

.

.

.

TABULKA XY str117 a 119

TABULKA XY str117 a 119

Pripojenie externej pamäti programu 2716:

Technické vybavenie potrebné pre pripojenie externej pamäti programu 2716 (EPROM 2 KB) k mikropočítaču 8031AH je na tomto obrázku:

OBR 48str 120

Pre zapamätanie ôsmich nižších bitov adresy je použitý obvod 8282

(osmibitový register s trojstavovými vstupnými budičmi). Vzhľadom na to,

že sa časť portu 2 využíva ako adresová zbernica, nie je možné vývody P2.3 až

P2.7 (v predchádzajúcom obrázku sú označené hviezdičkou) použiť ako vstupy

alebo výstupy.

Pripojenie externej pamäti programu 2732A:

Spôsob pripojenia externej pamäti programu 2732 (EPROM 4 KB) k mikropočítaču 8031AH je

znázornený na tomto obrázku:

OBR 49 str 121

Zapojenie je obdobou zapojenia paměti 2716 s tým rozdielom, že ďalší

potrebný adresový bit (A11) se generuje v bitu P2.3. Vývody P2.4 až

P2.7 portu 2 (v predošlom obrázku je označený hviezdičkou) opäť nie je možné

použíť ako vstupy alebo výstupy z dôvodov využitia časti portu 2 pre

adresovú zbernicu.

Pripojenie externej pamäti dát a expanderu V/V:

Externá

pamäť dát s kapacitou 256 B a expander V/V sú realizováné obvodom

8155. Jeho pripojenie k mikropočítaču 8051AH je na tomto obrázku:

OBR 50 str 122

Pre funkciu RESET obvodu 8155 môže byť využitá systémová

funkcia RESET alebo niektorá linka portov mikropočítača 8051.

..

![]() ..

..