- Základný princíp práce počítačov

- Bloková schéma mikropočítača

- Koncepcia Von Neuman

- Koncepcia Harward

- História mikroprocesorov série Intel 80x68 - adresovanie

- Práca s dátovými objektmi

- MIKROPOČÍTAČE (CZ)

- Nové pojmy

- Zdroje informácií

Architektúra mikropočítačov je založená na troch zberniciach vychádzajúcich z

CPU:

- ADRESNEJ ZBERNICI

- DÁTOVEJ ZBERNICI

- RIADIACEJ ZBERNICI

Čo sú to zbernice? Vo svojej podstate sú to

obyčajné paralelne vedené drôty ktoré sú číslované poradovým číslom

sprava doľava, tak ako je to zvykom v pozičných číselných sústavách.

Vodič najviac vpravo predstavuje 0-tý bit binárneho slova. Pozície rastú

smerom doľava. Vodiče zbernice spolu kódujú a prenášajú binárnu hodnotu.

Všetky zariadenia v počítači sú napojené na dátovú zbernicu súčasne.

Podľa charakteru či je to vstupné alebo výstupné zariadenie, v jeden čas môžu

spolu komunikovať len dve zariadenia. Napríklad pamäť ROM môže dáta

jedine vysielať. Pamäť RAM môže dáta aj vysielať aj prijímať. Výmenu dát

medzi ROM pamäťou a RAM pamäťou sprostredkuje procesor cez pracovné

registre. Najprv prenesie dáta z ROM pamäti do pracovného registra

mikroprocesora, a potom obsah tohto registra zapíše do RAM pamäte. Tento proces zabezpečujú všetky tri zbernice naraz.

DÁTOVÁ ZBERNICA je určená na prenos dát.

Podľa toho koľko paralelných drôtov dátová zbernica obsahuje rozpoznávame

triedu počítača 8, 16, 32 a 64 bitového.

ADRESNÁ ZBERNICA vysiela identifikačný kód

zariadenia. Adresovaná je každá bunka RAM pamäte, ale aj iné hardwarové

zariadenia. Adresa je však len jednou z podmienok prenosu dát. Na spustenie výmeny

dát to však nestačí. Spolu s adresou musí proces synchronizovať Riadiaca

zbernica.

RIADIACA ZBERNICA dáva konečný povel k

vykonaniu akcie.

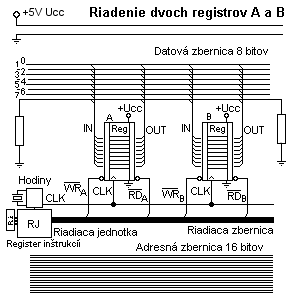

Nasledovný obrázok predstavuje funkčný model počítača, ktorý poslúži

na pochopenie konštrukcie a základný princíp práce počítačov.

|

Na obrázku vidíme napájace vedenia +5V a uzemnenie. Pod ním je dátová

zbernica s označenými vodičmi 0 - 7. Za vzor na obrázku slúži vodič

7 dátovej zbernice, ktorý má uzemnené oba konce odpormi cca 220 ohm. V

obrázku je naznačená adresná zbernica, a Riadiaca jednotka z ktorej

vychádzajú vodiče riadiacej zbernice. Riadiaca jednotka je napojená na

zdroj hodinových impulzov riadených kryštálom. Taktiež na vstupe RJ

sa nachádza Register inštrukcií, ktorý riadi chod riadiacej jednotky.

V obrázku sú ďalej zobrazené 3 modely zariadení:

- Spínač S7 zdroj logických stavov 0 a 1 - obdoba klávesnice

- Žiarovka ako signalizačný prvok stavu zbernice

- Bistabilný preklápací obvod - 7 bit registra A

Príklad: 1. Po stlačení tlačidla S7 chceme

aby sa napätie 5V prenieslo na zbernicu ako logická 1. Tento stav spôsobí

rozsvietenie žiarovky. Podmienkou je aby riadiace signály RD/s7

odblokoval výstup oddeľovača zbernice a zároveň WR/ž odblokoval vstup

oddeľovača zbernice aby signály prenikli.

Príklad: 2. Ak chceme zapísať stav tlačidlom S7 do

registra A, musíme vygenerovať riadiaci signál WR/a7 a počkať na

hodinový impulz CLK ktorý údaj do registra zapíše.

Príklad: 3. Ak chceme monitorovať stav registra

A, privedieme riadiaci signál RD/a7 na oddeľovač zbernice výstupu

registra - dáta sa prenesú na dátovú zbernicu - a signál WR/ž ktorý

odblokuje oddeľovač zbernice vstupu žiarovky Ž. |

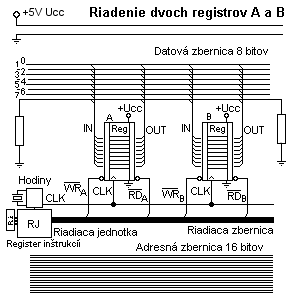

Nasleduje ukážka prenosu dát z registra A do registra B

|

V tomto

obrázku vidíme dva 8 bitové registre A a B. Oba majú prepojené aj

vstupy ale aj výstupy na dátovú zbernicu cez oddeľovače zberníc

riadené Riadiacou jednotkou. Kombináciou riadiacich signálov RD/a WR/b

odblokuje sa výstup A registra a vstup B registra. Príchod časového

signálu CLK zapíše hodnoty A registra do B registra.

Naopak riadiace signály RD/b

WR/a odblokujú výstup B registra a vstup A registra. príchod časového

signálu CLK zapíše hodnoty z B registra do A registra. |

Posledná ukážka ukazuje spoluprácu registra Acc s Aritmeticko Logickou

Jednotkou (ALU - Arithmetic Logic Unit)

|

Na obrázku vidíme špeciálny register Acc - akumulátor - v ktorom končia

výsledky matematických operácií ALU. Aritmetická logická jednotka má

dva pomocné registre na vstupe a jeden pomocný register na výstupe.

Tieto registre slúžia len na vykonanie operácie.

Pôvodné vstupné hodnoty môžu byť uložené

v registroch Acc a B napríklad. Riadiaca jednotka otvorí výstup jedného

z pracovných registrov a vstup pomocného registra "A"

na vstupe ALU - dáta prenesie. Potom to isté urobí s druhým operandom

"B". Vygeneruje príkaz na operáciu + alebo -.

Výsledok sa umiestni do pomocného výstupného

registra "C" ALU. nakoniec RJ otvorí vstup WR/a na zápis údaja

do Acc registra a RD/c na prenesenie výsledku. |

Skutočnú architektúru mikropočítačov Von

Neumannovho typu ukazuje nasledovný obrázok:

Počítač Von Neumanna používa

jednu pamäť pre program aj pre dáta

a jeho jadrom je Centrálna procesorová

jednotka - CPU (Central procesor unit) -

do ktorej sa prenášajú a spracovávajú dáta z pamätí (RAM, HD, FDD,

CD, ...) a vstupných

jednotiek podľa programu (softwéru) uloženého v Operačnej pamäti (OP)

(OM - Operating memory). Operačnú pamäť realizuje pamäť RAM (Random access memory)

t.j. pamäť s náhodným prístupom, ktorá má dočasný charakter, a po

vypnutí napájania počítača stráca svoj obsah.

Počas vykonávania programu sa jednotlivé inštrukcie z

operačnej pamäti, v poradí ako sú v OP uložené, postupne prenášajú do

CPU do registra inštrukcií v ktorom sa inštrukcie

dekódujú a vykonávajú . Na ich adresovanie slúži programový

čítač inštrukcií (PC), ktorý sa počas vykonávania inštrukcie

automaticky inkrementuje (zvyšuje) o dĺžku vykonávanej inštrukcie, tak že

pred začiatkom nasledovného inštrukčného cyklu ukazuje na začiatok

nasledovnej inštrukcie ktorá sa bude vykonávať. Túto postupnosť môžu

zmeniť tzv. skokové inštrukcie, ktoré samé vložia nový obsah do programového

čítača a umožňujú pokračovanie programu od inej adresy.

Centrálna procesorová

jednotka - CPU (Central procesor unit) sa skladá z :

- programového čítača inštrukcií - registra

PC (Program Couter)

- register inštrukcie RI

- akumulátora (A register

resp Acc)

- aritmetickej logickej jednotky (ALU - Arithmetic

Logic Unit)

- systému 3 zberníc - dátovej,

adresnej a riadiacej

Programový čítač inštrukcií - je register slúžiaci na

adresovanie nasledovnej inštrukcie, ktorá sa bude vykonávať po ukončení práve vykonávanej

inštrukcie. Jeho obsah sa inkrementuje v prvých taktoch vykonávania aktuálnej

inštrukcie. Inkrementácia závisí od operačného kódu

inštrukcie, ktorý určuje koľko slovná

je práve vykonávaná inštrukcia.

Inštrukčný register - je miesto do ktorého sa inštrukcia z

operačnej

pamäti presunie počas Inštrukčného cyklu

a ktorá určuje ďalšiu činnosť riadiacej jednotky procesora.

Akumulátor - je register úzko spolupracujúci s aritmeticko

logickou jednotkou, v ktorom sa nachádza jeden z operandov a do ktorého sa

ukladajú výsledky aritmetických a logických operácií.

Aritmetická logická jednotka - je obvod v

procesore, ktorý má dva

vstupy a jeden výstup. Vykonáva operácie sčítania, odčítania, inkrementácie

o 1 a dekrementácie o 1, operácie logického súčtu, logického súčinu a

negácie ako aj operácie EXCLUSIVE OR t.j. NON EKVIVALENCIE.

Architektúra počítača je sústredená okolo obojsmernej

dátovej zbernice po ktorej sa prenášajú dáta aj inštrukcie.

Zbernica je n-bitová, kde n je dĺžka

strojového slova a pre daný typ počítača je konštantná. (8- bitové

počítače, 16- bitové počítače, 32- bitové počítače, 64- bitové

počítače, ?- ...)

Inštrukčný cyklus - (t.j. čas za ktorý sa vykonajú inštrukcie v

počítači Von Neumanna) sa skladá z týchto činností

Inštrukčný cyklus - (t.j. čas za ktorý sa vykonajú inštrukcie v

počítači Von Neumanna) sa skladá z týchto činností

- vyslanie adresy inštrukcie na ktorú ukazuje PC register.

- prenos inštrukcie z pamäti do registra inštrukcií

RI

- dekódovanie inštrukcie

- nastavenie nového obsahu PC registra

- vykonanie inštrukcie

Inštrukčný cyklus končí prechodom na ďalšiu inštrukciu

Algoritmus inštrukčného cyklu.

Typické znaky architektúry riešenia Von Neumanna:

- pevná inštrukčná sada

- pevný operačný kód

- pevný dekodér inštrukcií.

Ukážkovým predstaviteľom Von NEUMANNOVSKEJ koncepcie je mikroprocesor

I8080 ktorý bol zakladateľom následnej rady procesorov I8088, I8086,

I808286,I80386, I80486, Pentium, Celeron, ... a zo stajne AMD ... klony

I80286-486, Durony a Athlony používané v počítačoch typu IBM PC AT a

ATX.

Harwardská architektúra používa dve oddelené pamäti

pre dáta a program. t.j. pamäť dát a riadiacu pamäť.

Riadiaca pamäť - obsahuje informácie o riadení systému. Tieto

informácie dekóduje riadiaca jednotka. ktorá zabezpečuje následnosť

výberu riadiacich signálov z riadiacej pamäti.

Podstatnou charakteristikou tejto architektúry je, že zmenou obsahu

riadiacej pamäti je možné meniť riadenie systému, t.j. meniť inštrukčnú

sadu systému a operačný kód a teda programovať na úrovni riadiacich signálov.

Tieto postupy tvoria podstatu mikro-programovania.

| |

|

|

|

Principiálna schéma Harwardskej konfigurácie. |

|

|

|

|

|

|

|

| |

|

|

Rozdiely v dvoch koncepciách spočívajú v týchto

znakoch:

- PC register u von NEUMANNovskej koncepcie adresuje

RAM pamäť a u HARWARDskej adresuje

ROM pamäť.

- Na rozdiel od von NEUMANNovskej koncepcie

HARWARDská nemá

v inštrukčnom cykle krok prenášajúci kód inštrukcie z RAM

pamäte do Registra inštrukcií. ROM

pamäť supluje funkciu Registra inštrukcií. Jej výstup je priamo

napojený na RJ a tak stačí mať

v PC registri adresu inštrukcie,

ktorá sa bude vykonávať.

- U von NEUMANNovskej koncepcie v RAM sa

nachádzajú inštrukcie aj dáta

(t.j. premenné aj konštanty),

u HARWARDskej sa v RAM

nachádzajú z len premenné dáta a

v ROM

sa nachádzajú inštrukcie

a z dát len konštanty

(zapisujú sa tam spolu s programom).

Procesor I8051 je jedným z najpopulárnejších

mikroprocesorov Harwardskej koncepcie - ktorý

je zároveň aj najmenším mikropočítačom. Prečo? Lebo v sebe obsahuje všetko

čo mikropočítač potrebuje ku svojej práci:

- *CPU - (Central procesor unit)

- Register inštrukcií (RI) - obsahujúci

vždy práve vykonávanú inštrukciu počas jej inštrukčného cyklu.

- *Riadiaca jednotka (dekodér inštrukcií

/ktorý dekóduje inštrukciu

v RI/ + Radič - automat vykonávajúci

samotný priebeh inštrukcie a riadiaci procesy cez riadiacu zbernicu.

- Program counter (PC) - register obsahujúci

adresu inštrukcie v programe ktorá sa bude práve vykonávať

- *Aritmeticko - logická jednotka

(Arithmetic logic unit - ALU) - vykonávajúca všetky aritmetické a logické operácie medzi

operandami v pracovných registroch

- Akumulátor - hlavný pracovný register

spolupracujúci s ALU - zúčastňuje sa operácií ALU a v ňom končia

výsledky

- *Register príznakov - Program status word

(PSW) - uchovávajúci vyhodnocujúce príznaky operácií v ALU - riadi

podmienené skokové inštrukcie

- Register zásobníkovej pamäti -

Stack pointer (SP) - v RAM pamäti vytvára odkladacie miesto pre dáta

metódou Posledný dnu - prvý von LiFo(last IN First out)

- RAM - Random access memory -

prepisovateľnú pracovnú DÁTOVÚ pamäť s náhodným prístupom (tzv.

DATA memory z hľadiska programu).

- ROM - Read only memory - pamäť určená

len pre čítanie - obsahujúcu KÓD programu (tzv. CODE memory z hľadiska

programu)

- Špeciálne periférie:

- Radič prerušení -

obvody reagujúce na podnety externých periférnych zariadení

- Čítače (dva) - umožňujúce odmeriavať

presné časové intervaly

- Sériový komunikačný kanál (sériový

port - t.j. bránu) - univerzálna komunikačná linka umožňujúca štandardné

prepojenie s inými počítačmi a zariadeniami

- Vstupno - Výstupné brány (štyri 8

bitové V/V registre P0,P1,P2,P3) - umožňujúce komunikovať cez

paralelné linky s externými zariadeniami rozširujúce mikropočítač

o ďalšie externé periférne zariadenia (HD, CD, FDD, RAM, ROM, Tlačiarne,

zobrazovací Monitor, ....). Pri takomto rozširovaní sa brány špecializujú

na vyvedenie vnútorných zberníc - dátovej, riadiacej a adresnej

takto:

- P0 - prenáša počas jedného

inštrukčného cyklu striedavo 8 nižších

bitov adresnej zbernice a 8 bitov dátovej

zbernice a to tak, že adresu signalizuje signál ALE, a dáta

signalizuje jedným zo signálov /RD, /RW (pre zariadeniam typu

RAM), alebo /PSEN (pre zariadeniam typu ROM) podľa určenia.

- P1 - je univerzálny port k voľnému

použitiu

- P2 - prenáša trvalo bez prerušovania

počas jedného inštrukčného cyklu

8 vyšších bitov adresnej zbernice

- P3 - prenáša

počas inštrukčného cyklu časť

signálov riadiacej zbernice /RD

a /WR a

signály špeciálnych periférií

(viď. * v

obrázku)

- Číslicové elektronické systémy - Ing. Dušan Levický, Skriptá VŠT

Košice, 1982

- Uživateľská příručka mikropočítačů řady 48 - Ing.Vojtech Mužík

a kolektiv, ČSVTS 1985

RAM - Random access memory

CPU- Central procesor unit.

HD- Hard disk

FDD- Floppy disk drive

CD - Compact disk

Author Ing. JANOUŠEK Jaroslav.

Copyright © 2003

ManINFO -

Košice. All rights reserved.

Revised: januára 10, 2009

.

Inštrukčný cyklus - (t.j. čas za ktorý sa vykonajú inštrukcie v

počítači Von Neumanna) sa skladá z týchto činností

Inštrukčný cyklus - (t.j. čas za ktorý sa vykonajú inštrukcie v

počítači Von Neumanna) sa skladá z týchto činností